软件设计师中级

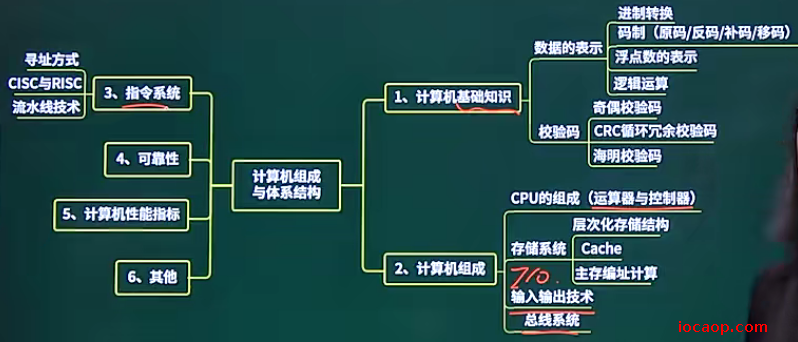

1.1-数据的表示

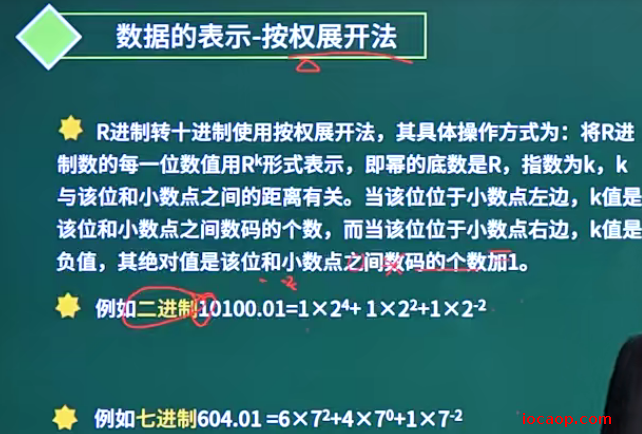

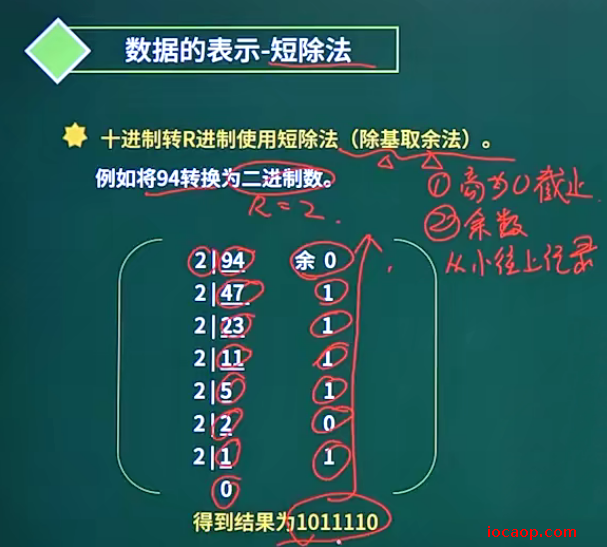

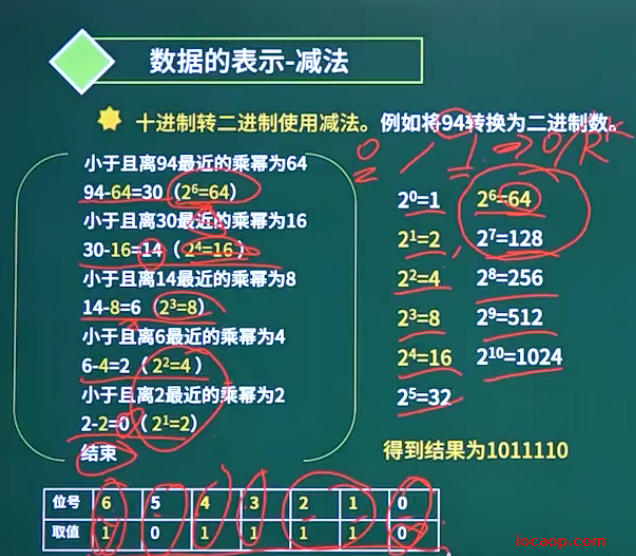

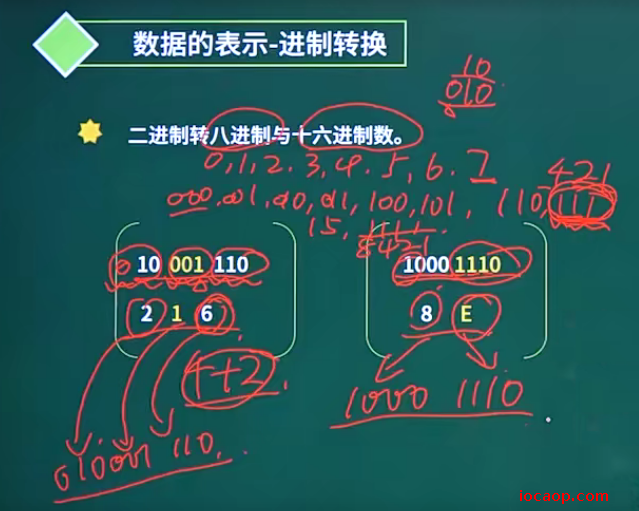

1-1-2-进制转换

(可选):

1.1.3-码制

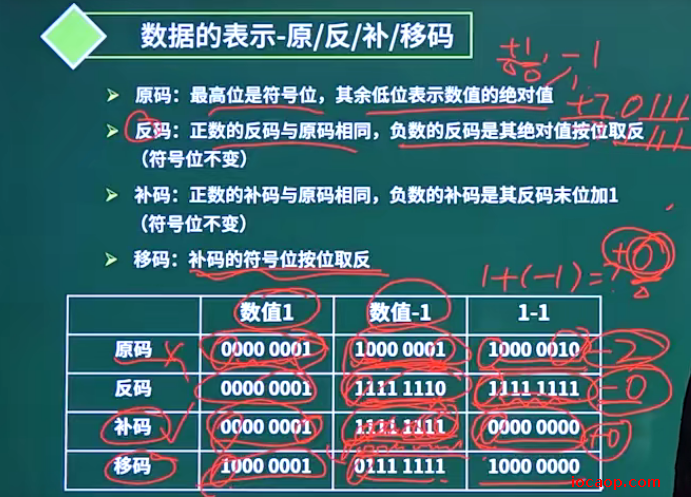

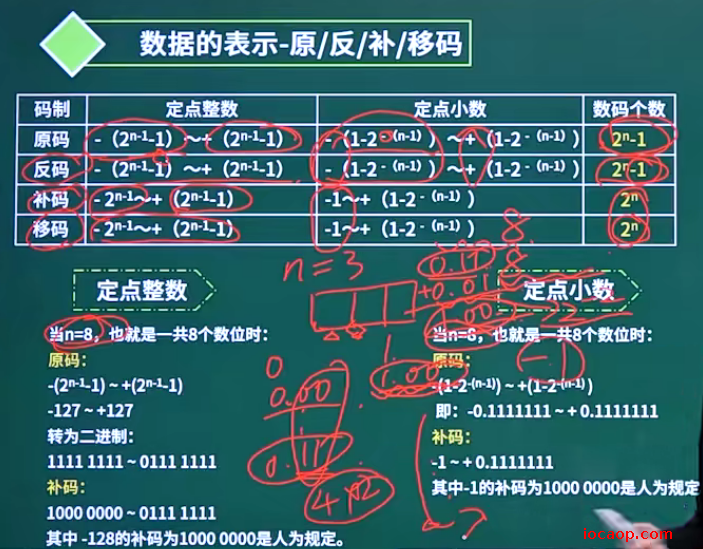

原反补:注意反码(正数反码和原码一样)。移码是符号位取反

注意定点整数补码的-128(原码中的+0和-0)和定点小数的-1是人为规定。

例题:

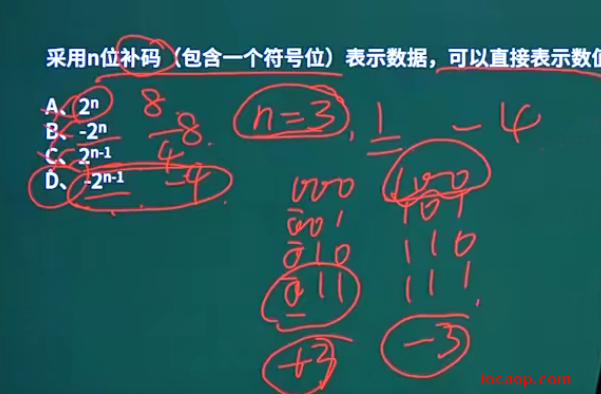

1.注意人为规定取值-4

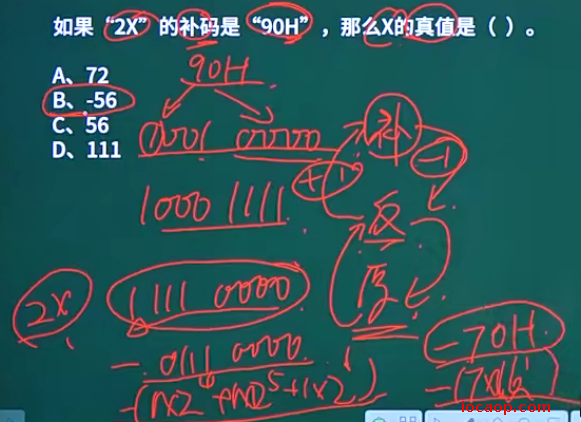

2.注意补码求原码,先看符号位,负数求反码(取反加1即可,不用按视频中的-1,用上模的概念),再求补码

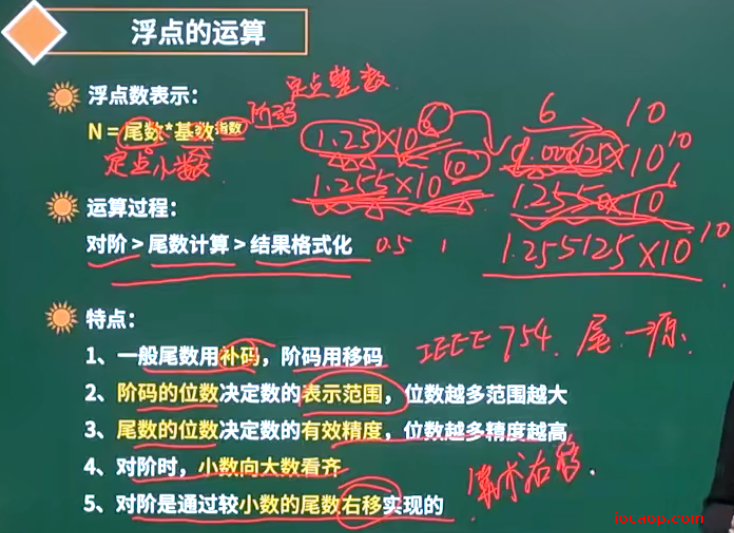

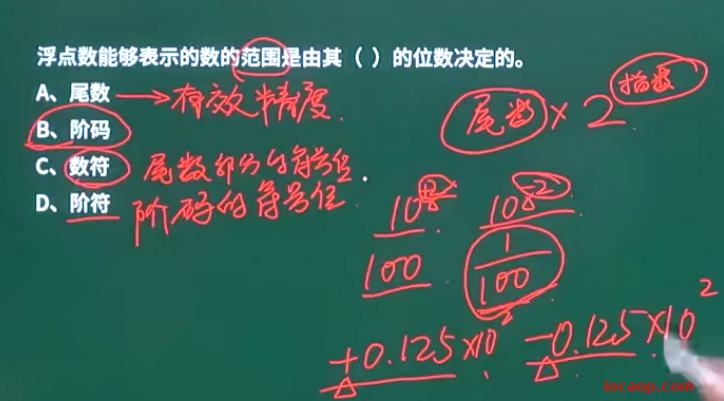

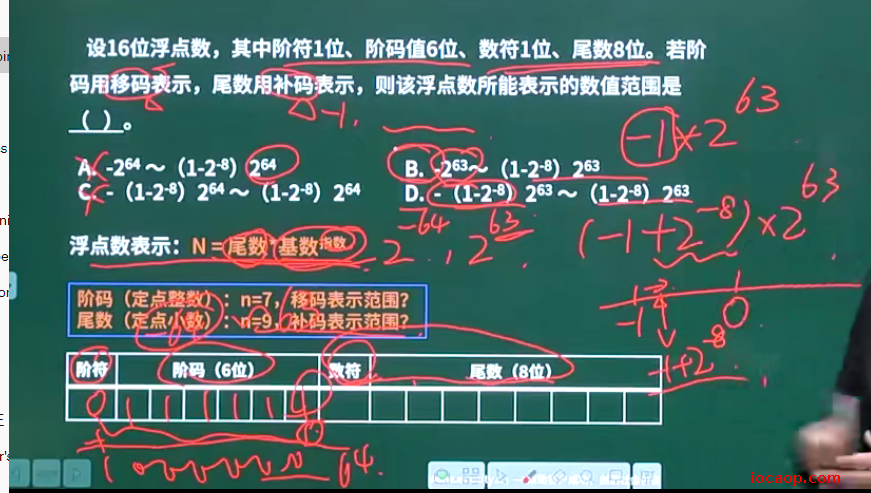

1.1.4-浮点数表示

考试时概念居多:

例题:

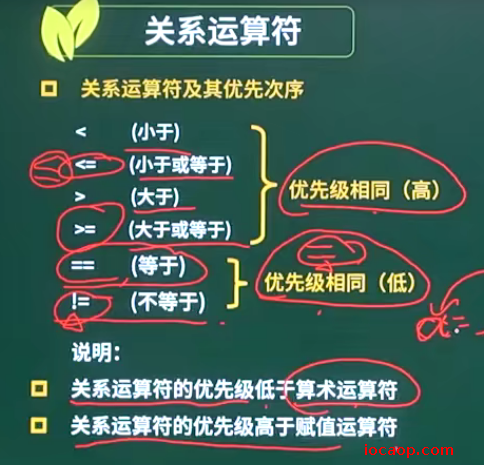

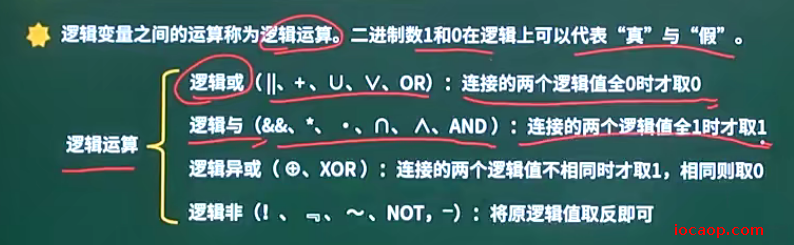

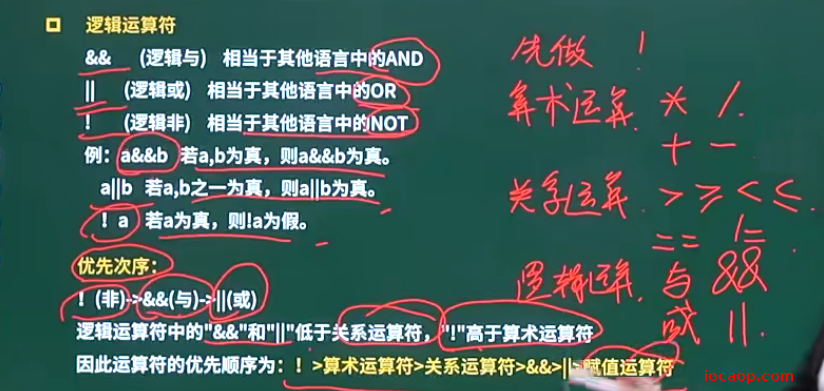

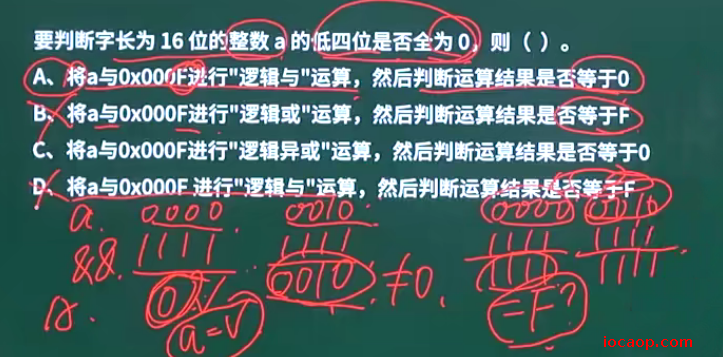

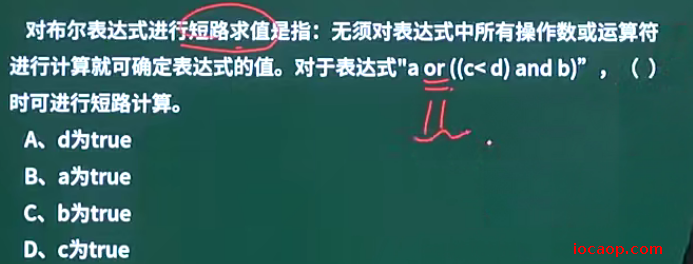

1.1.5-逻辑运算

例题:

1.2-校验码

1.2.1-概述

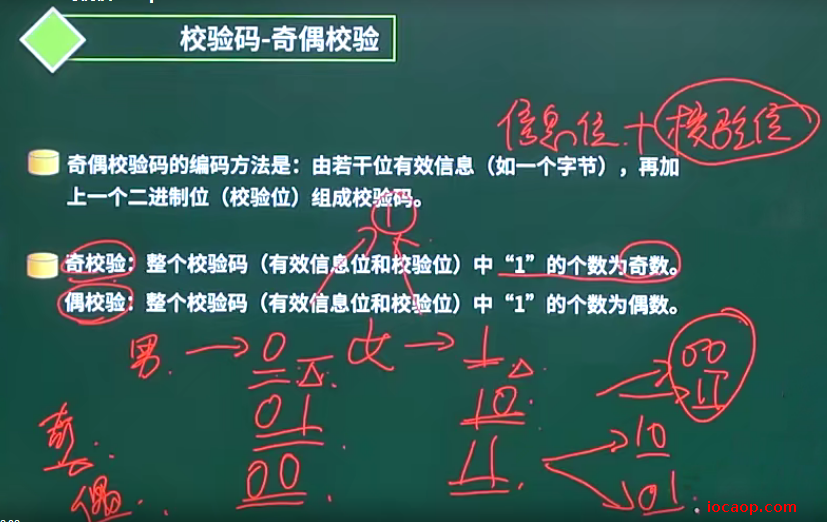

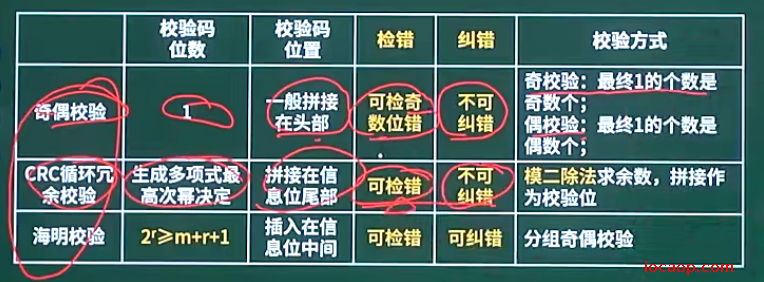

1.2.2-奇偶校验

为什么要有校验码?防止发送过程中,数据错乱,0变为1或者1变为0了,和原来不一样了。在原有的信息基础上增加冗余信息,帮助校验。

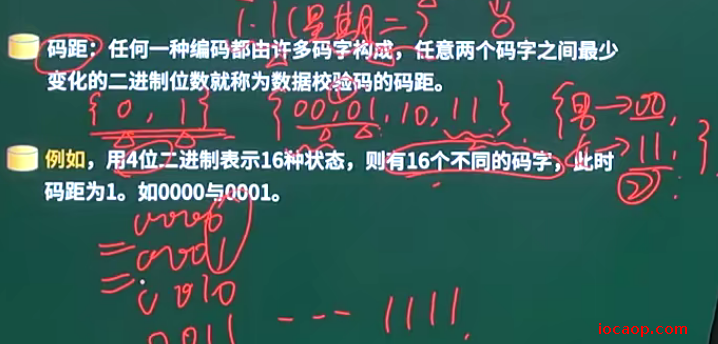

码字的码距:两个码字的码距是一个编码系统中任意两个合法编码(码字)之间不同的二进制数位数

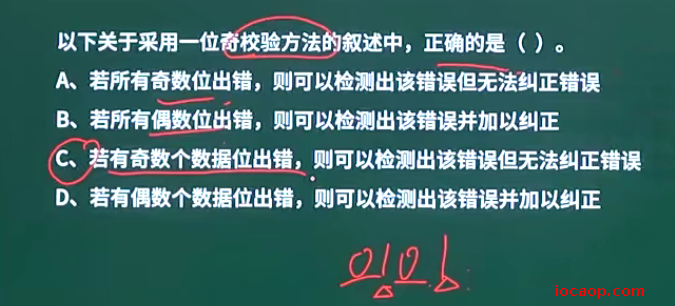

奇偶校验有局限性,如发送00,接受到11,校验不出来,且不能纠错。

例题:

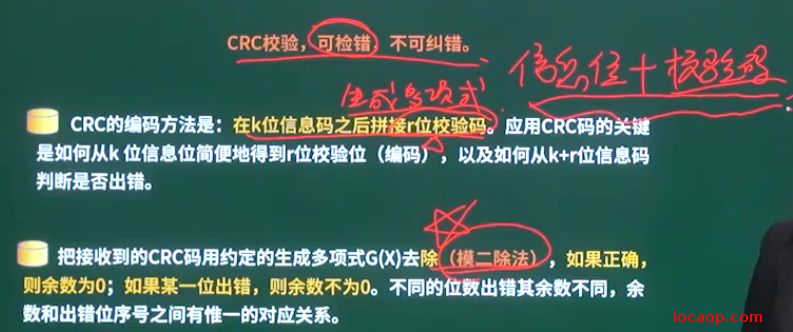

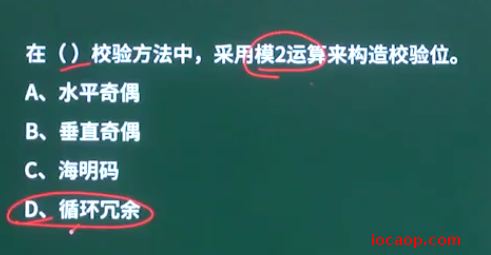

1.2.3-CRC冗余校验

中级考试不涉及编码求取。

例题:

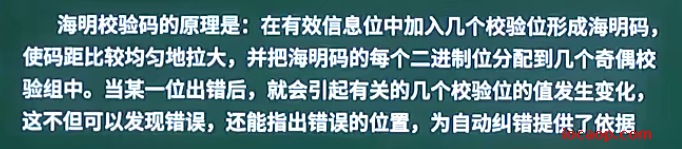

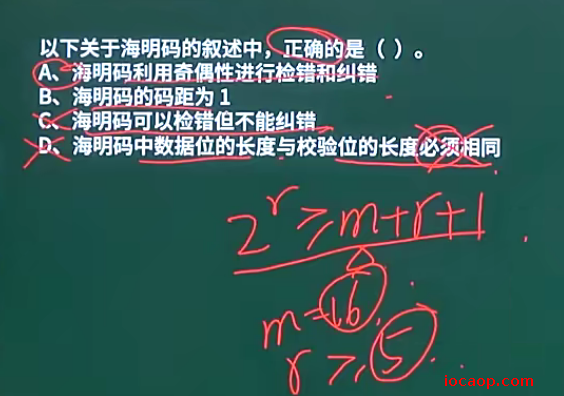

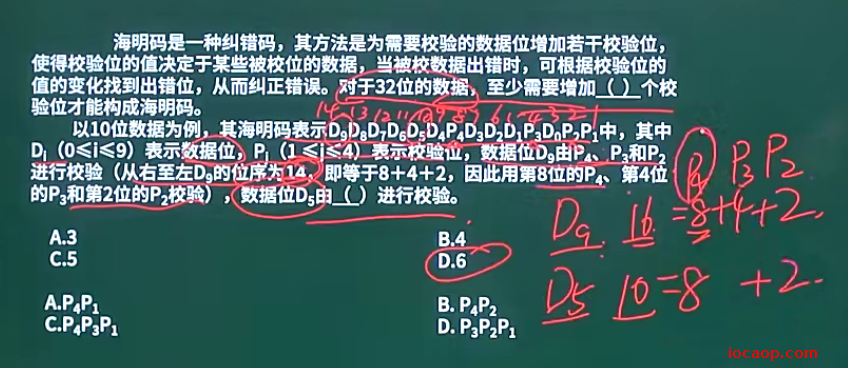

1.2.4-海明校验

即可检错,也可纠错

海明校验码位数求取:

2^r >= m+r+1,r是校验位位数,m是信息位位数

例题:

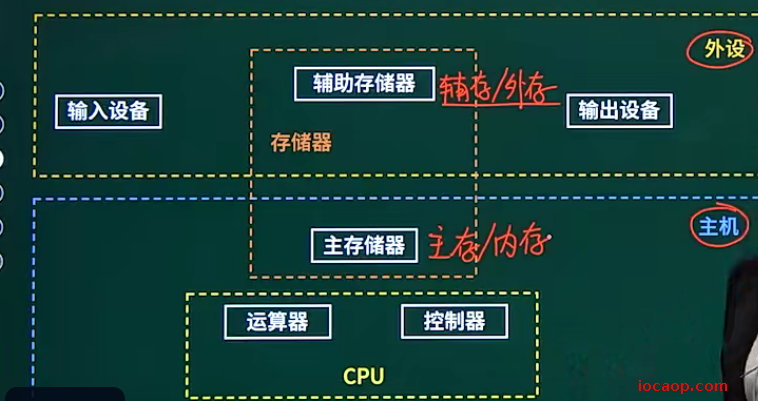

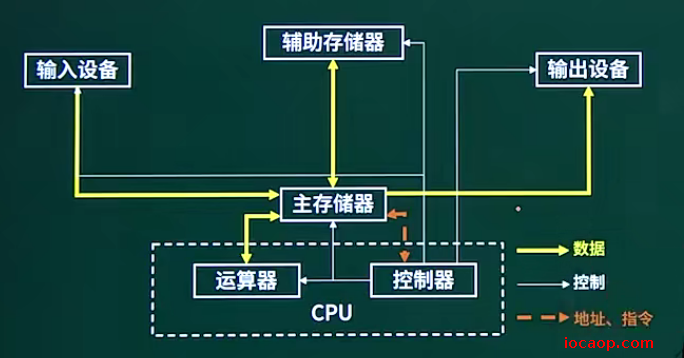

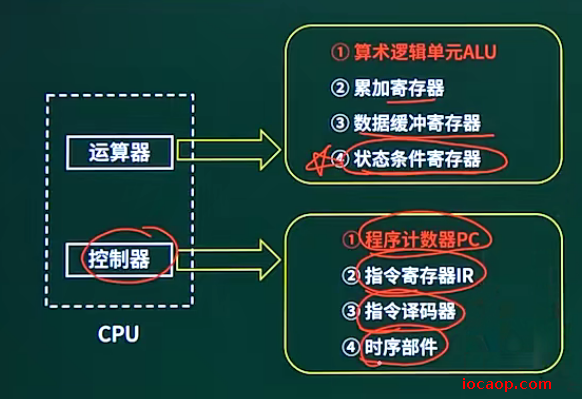

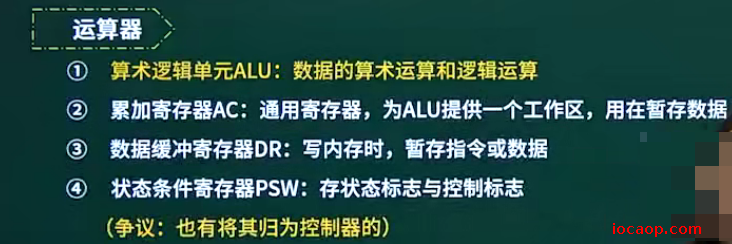

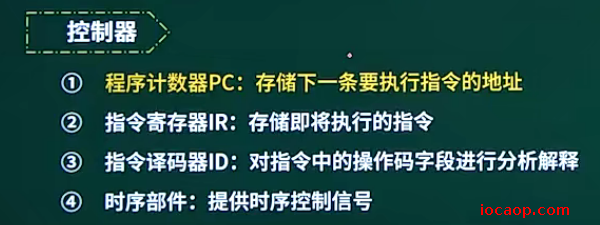

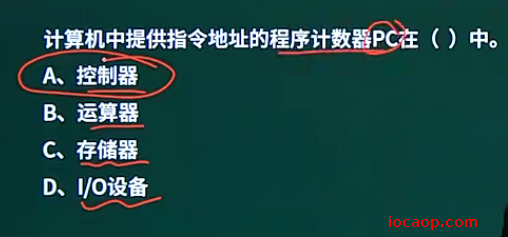

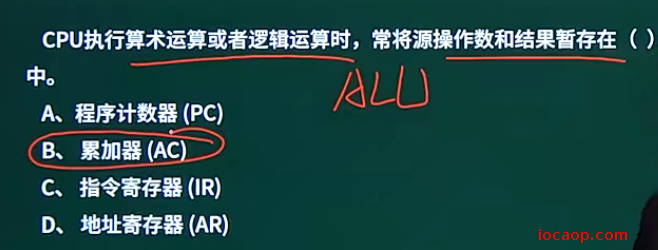

1.3-CPU组成(控制器与运算器)

状态条件寄存器的分类存在争议,也可以划分到控制器中。

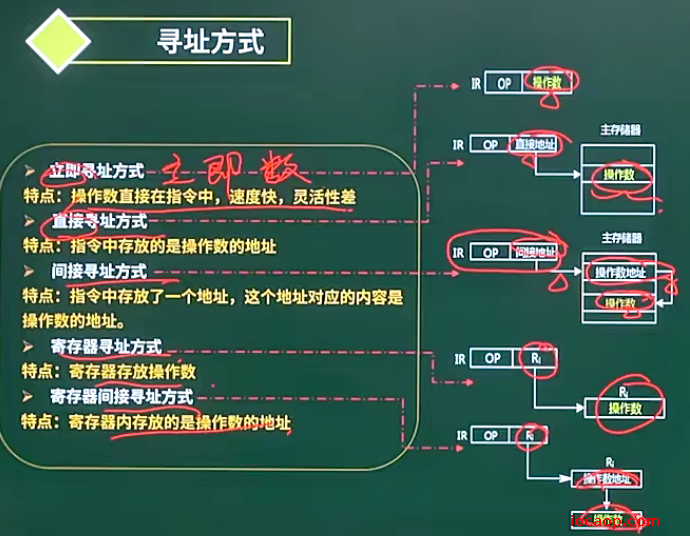

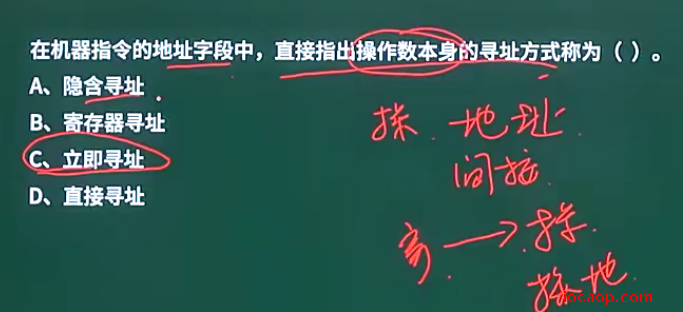

1.4-寻址方式

例题:

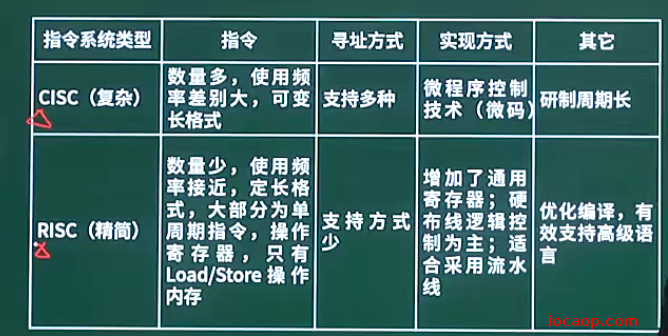

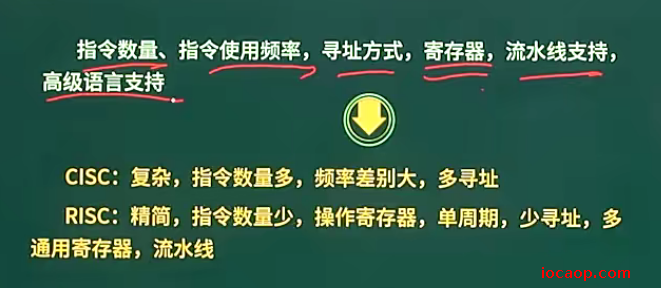

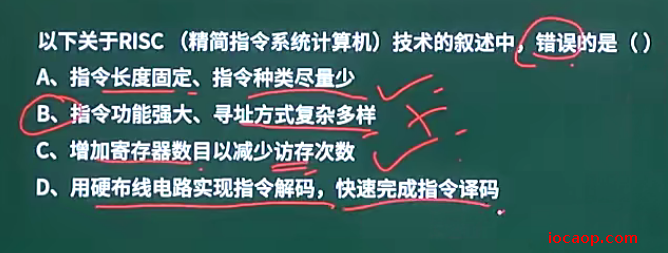

1.5-CISC和RISC

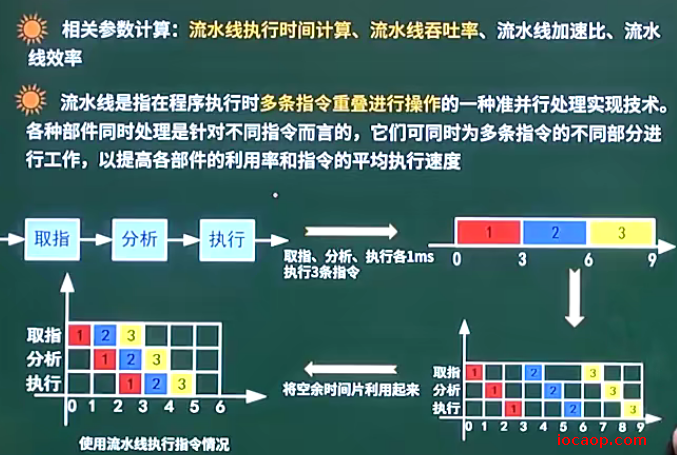

1.6-流水线

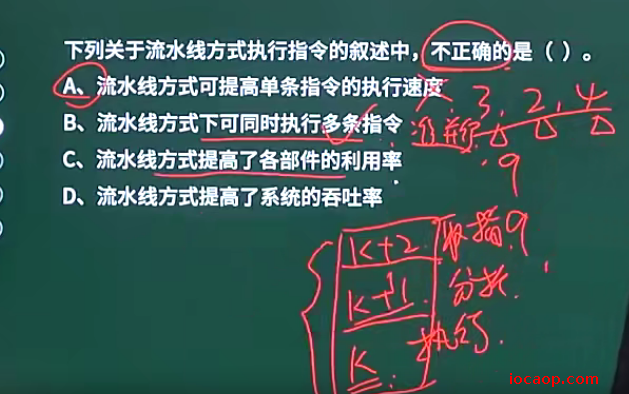

流水线是准并行

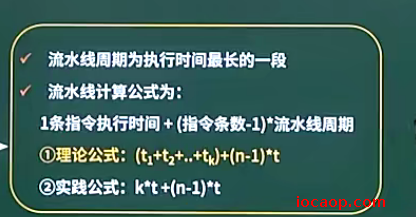

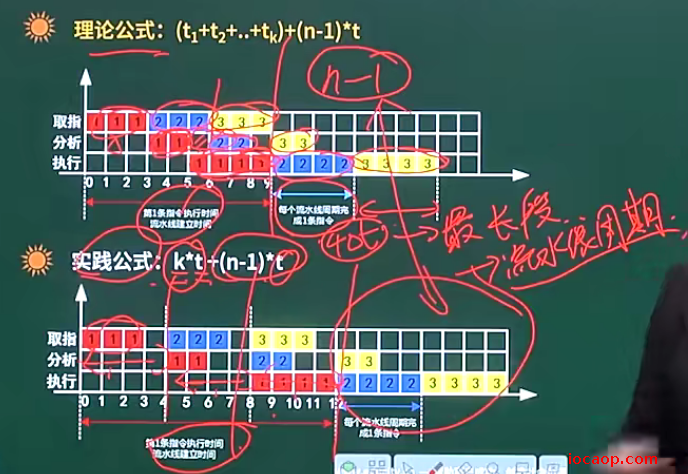

周期为执行时间最长的阶段的时间,k为执行过程分解为几步,n为指令条数

默认使用理论公式,没有再用实践公式

理论公式的理解:由图所示,在进行1的取指后,同时进行1的分析和2的取指,在进行完1的分析后执行1的执行,但是需要等待2的取指完成再进行2的分析,然后在1的执行完成后进行2的执行。最后,由图可得,最下面(2222,3333),每个流水线周期完成1条指令是4△t,所以:

总时间为第一个指令的总时间,加上后面所有任务的时间(数量*周期时间),周期时间是执行周期最长的一段

*(t1+t2+t3+...+tk)+(n-1)t

实践公式:和理论公式类似,但是第一个任务的时间是按每个阶段都以指令周期来算(最长的一段),所以公式是k*t+(n-1)*t

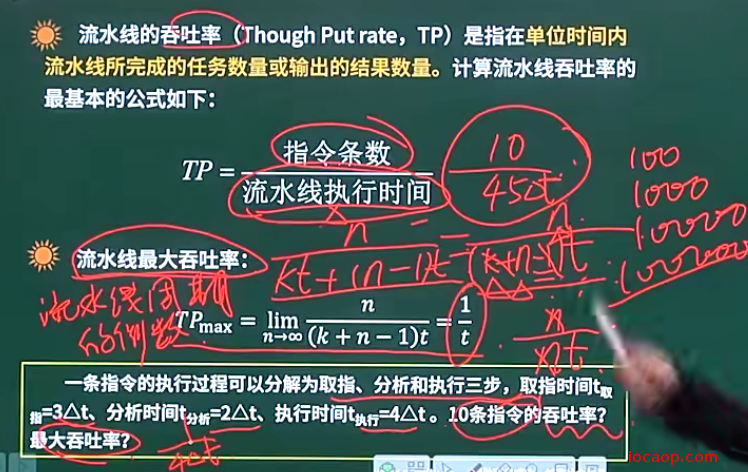

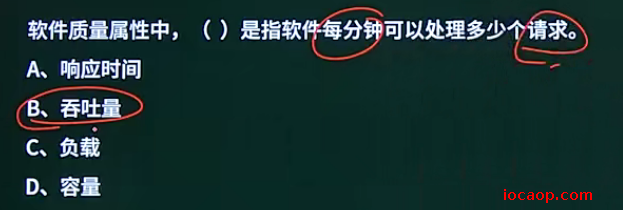

吞吐率:指令条数/执行总时间

最大吞吐率计算:指令周期的倒数

例题:

1.7-存储系统

1.7.1-概述

1.7.2-层次化存储

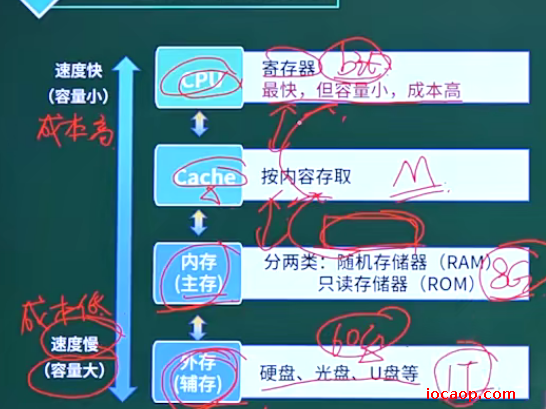

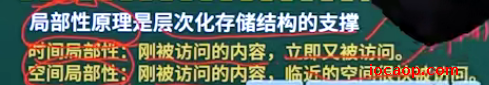

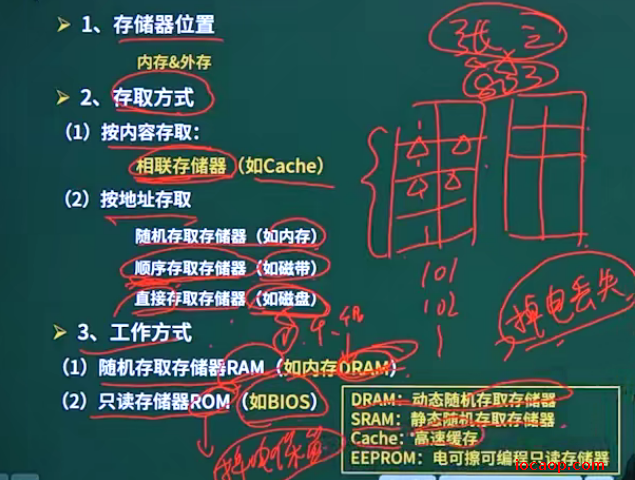

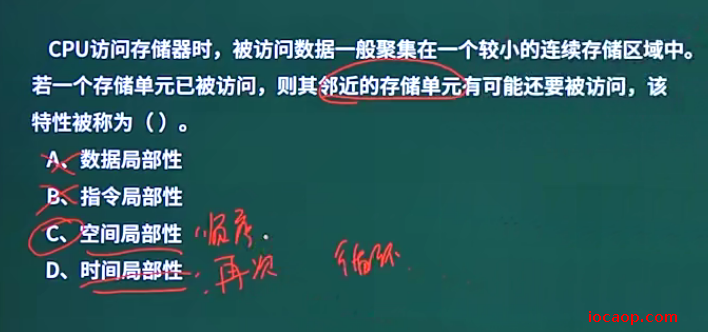

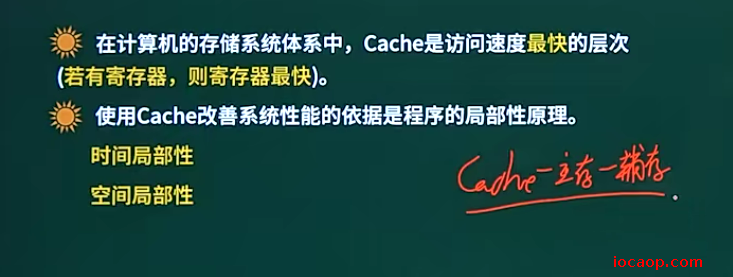

三级存储体系:cache+内存+外存

相联存储器:是一种不根据地址而是根据存储内容来进行存取的存储器。点击跳转

SRAM 在工作时不需要刷新,而 DRAM 在工作时需要定期刷新,否则数据就会丢失。

例题:

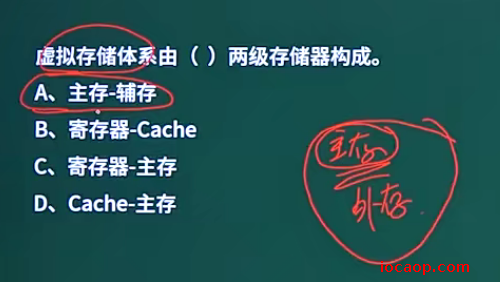

虚拟存储体系:主存不够时,用外存。点击跳转

1.7.3-Cache

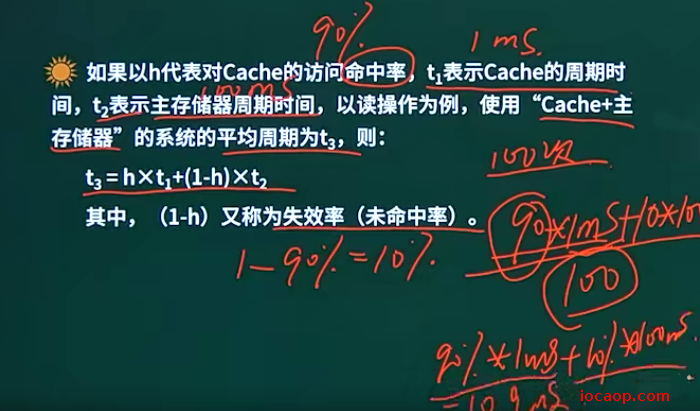

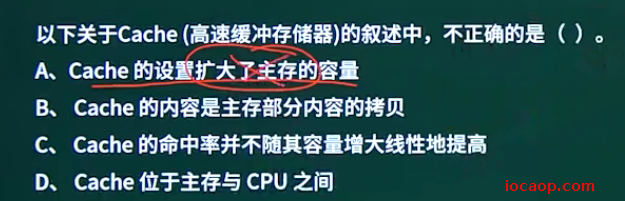

公式含义:平均周期=命中率*cache周期时间+未命中率*主存周期时间

从主存复制了一部分数据到Cache中。

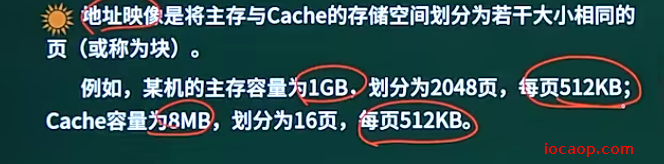

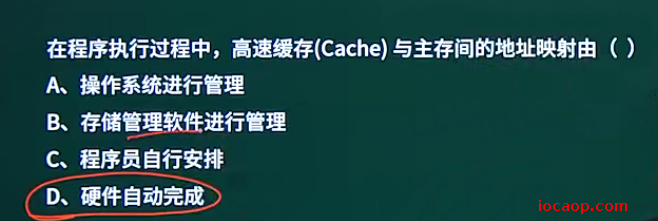

地址映象:

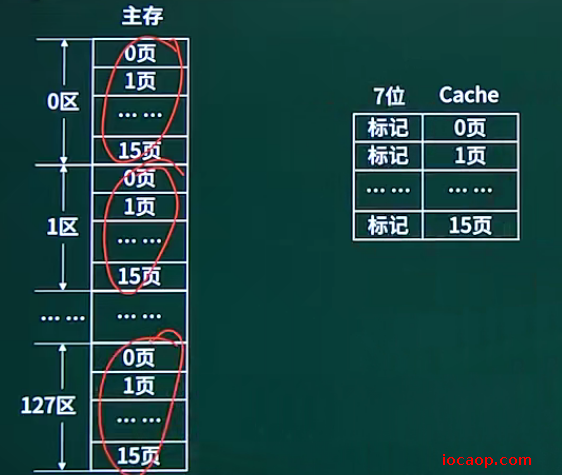

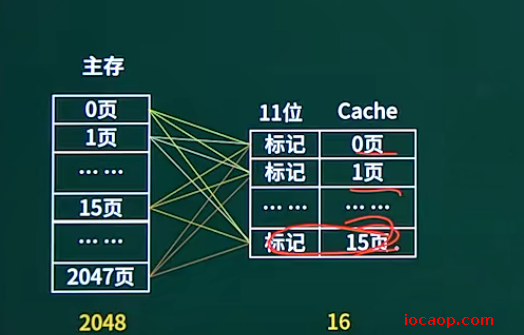

如何将2048个页放到16个页中?具体怎么映射(不需要操作系统和程序员参与):

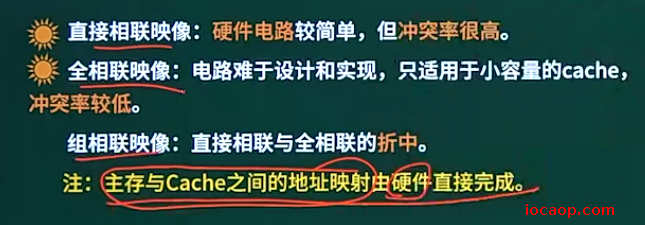

直接相联映像:

将主存划分成n个与Cache相同大小的区域,每个区域和cache一样,有16个页。

每个区域的0号页都与cache的0号页映射,1号也是如此,以此类推。

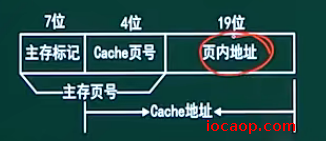

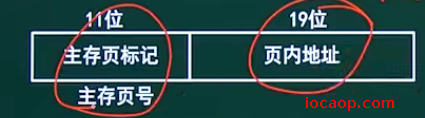

此时,主存的地址格式:

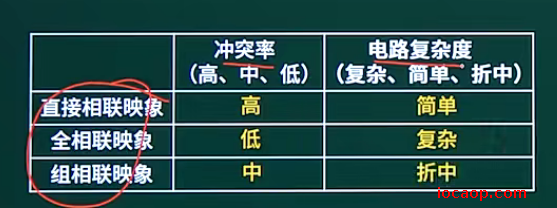

电路实现简单,但是冲突率高。

什么是冲突?当我们将0号区的0号页放到cache的0号页,就不能将其他区的0号页放到cache,否则就会冲突。

极端情况:把0号区0-14号页都放入cache,那么就只有127个区的15号页可以放入cache,有2048-15(0-14页已放入的)-128(15页可放入的)个页不能放入cache,冲突了。冲突率可以达到90%

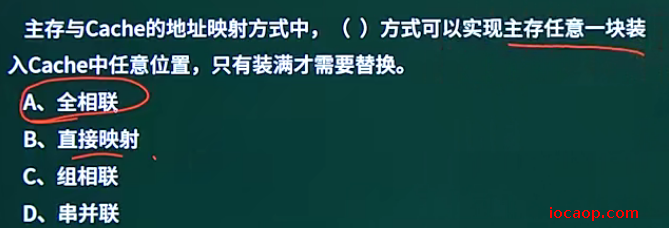

全相联映像

主存中的任意页可以放到cache中的任意页。

主存地址格式:

电路复杂,冲突率低

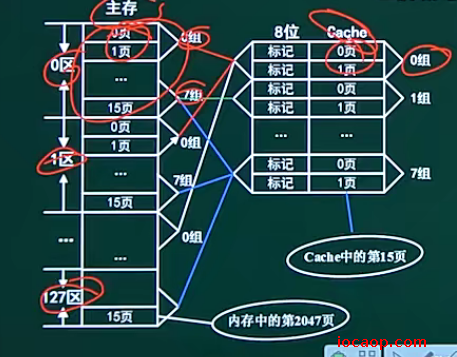

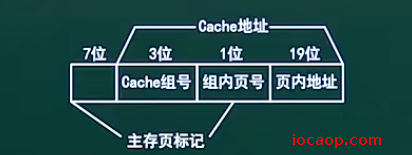

组相联映像

主存按cache的页的大小进行分页,分完页再分区。在这些区中,再进行分组,每组2个页,对应cache中也是如此。

相同组号的主存中的任意页面可以放到相同组号的cache的任意页面。

主存地址格式:

电路复杂度相对其他两种,折中,冲突率也是折中。

总结:

例题:

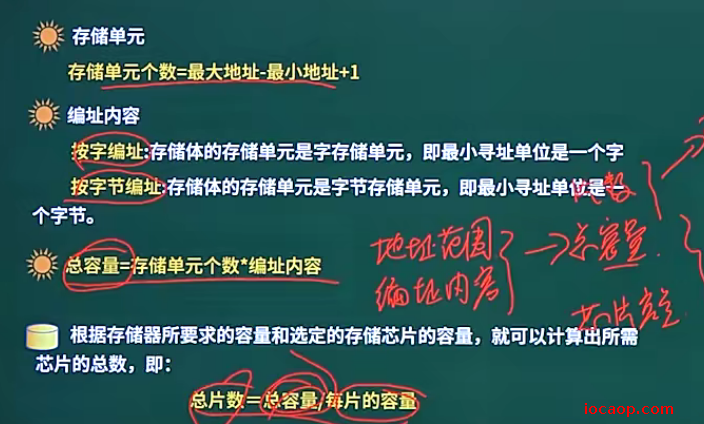

1.7.4-主存编址计算

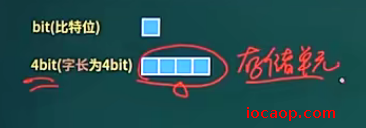

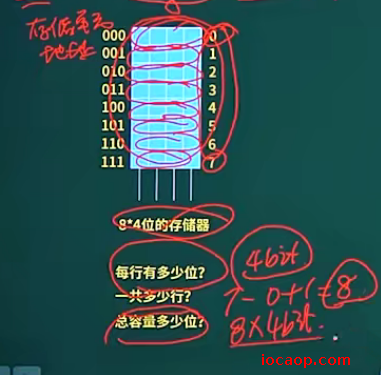

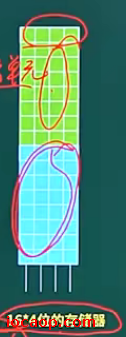

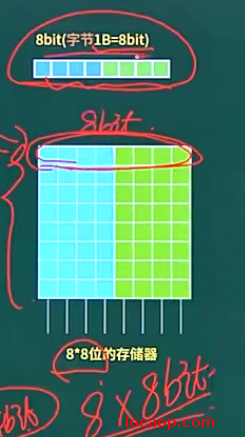

在计算机中找到一个位是很麻烦的,但是找到一行就很简单了,将4个比特位作为一行,也叫存储单元,找起来就简单多了。

一般是32个字节,考试中是16个字节(如果没给出,默认32)。

垂直拼接:

水平拼接:

公式:

例题:

解析:

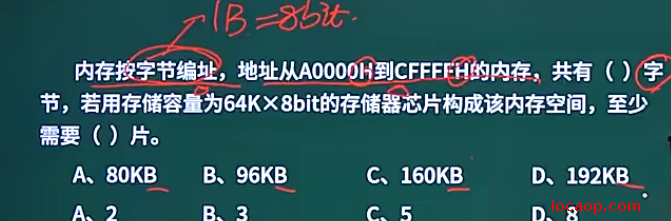

第一空:

求总容量:

- 给了地址范围可以求出存储单元个数:

CFFFFH-A0000H+1可以先算后面的加1,变成D0000H-A0000H=30000H,也就是3*2^16个存储单元。

- 题干说内存按字节编址,1B=8bit。选项容量单位是KB,存储单元个数化成K=3*2^10*2^6=3*2^6K,本身就是字节编址,所以总容量就是3*2^6KB=192KB

第二空:

用64K*8bit的存储器芯片构成192KB的空间,则:

芯片数:总容量/单位芯片容量

192KB/64KB=3

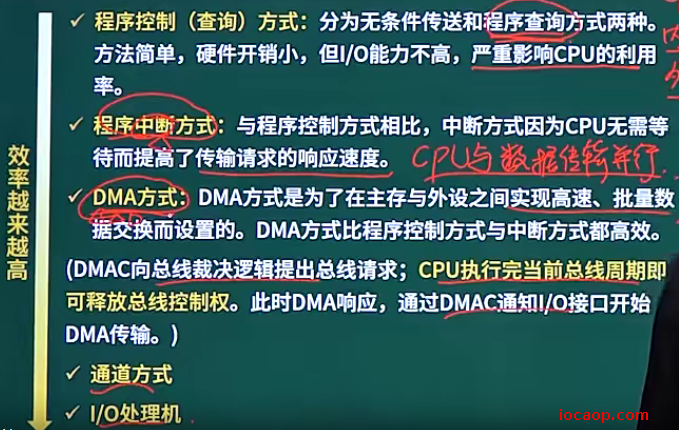

1.8-输入输出系统

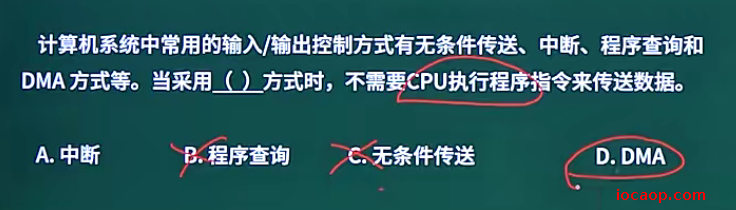

cpu控制数据传输,io是内存和外设之间的数据交互,内存较快,外设较慢。

程序查询方式是cpu一直查询外设,进行询问。

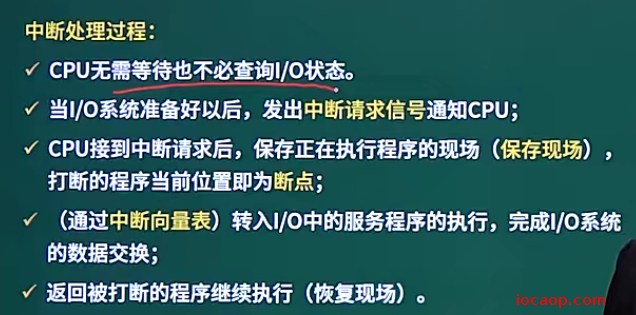

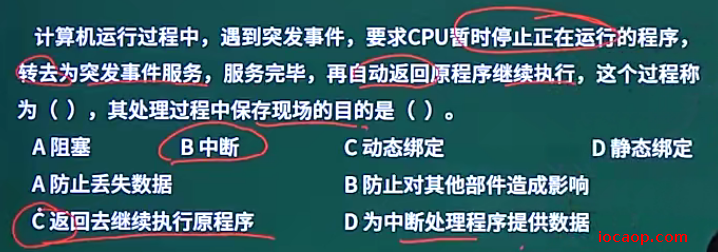

中断方式是需要io时中断,没有中断时cpu可以做其他事,中断操作之后可以继续做其他事:

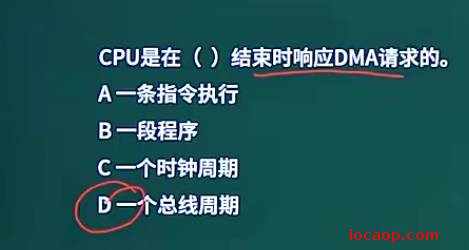

DMA无需cpu参与,由DMAC进行,点击跳转

例题:

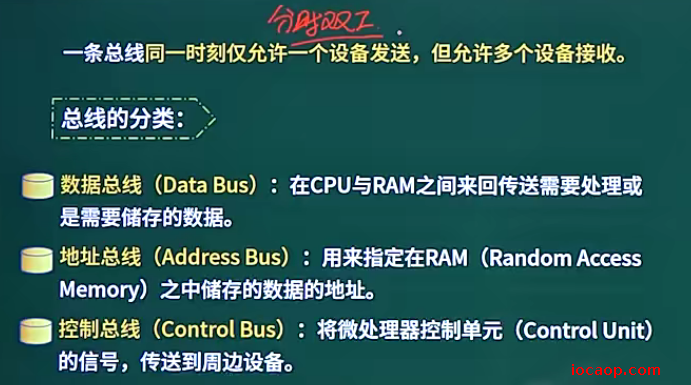

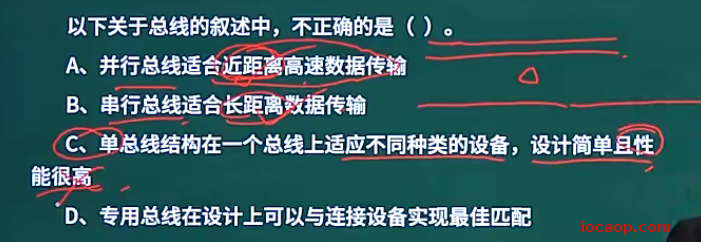

1.9-总线系统

例题:

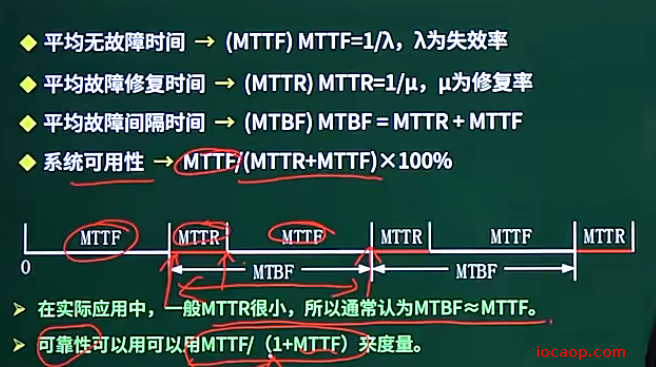

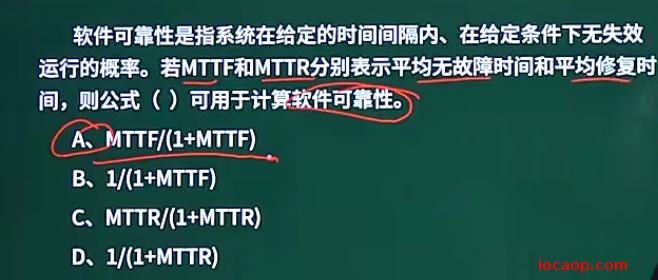

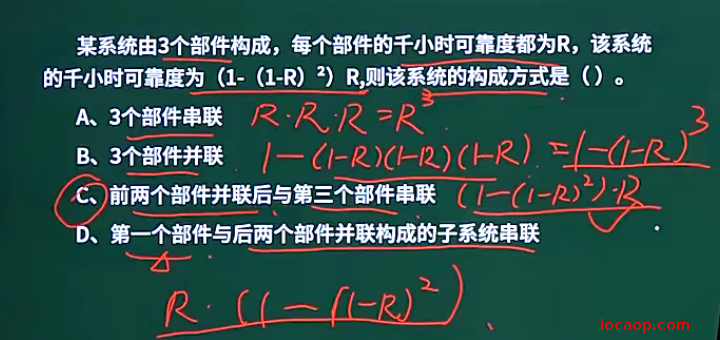

1.10-可靠性

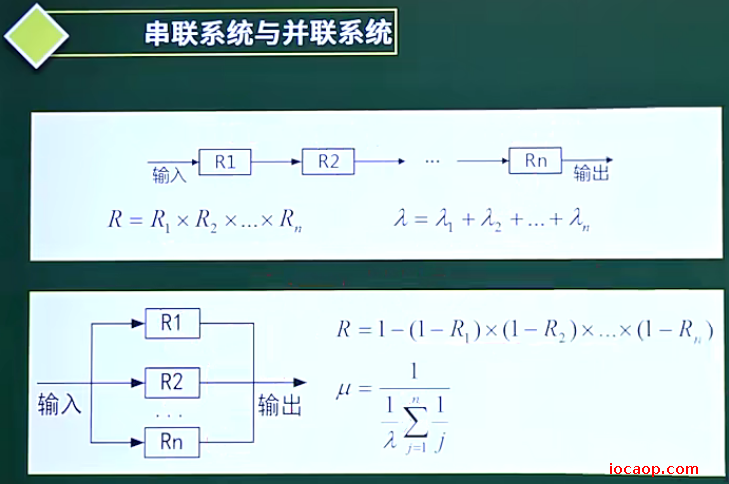

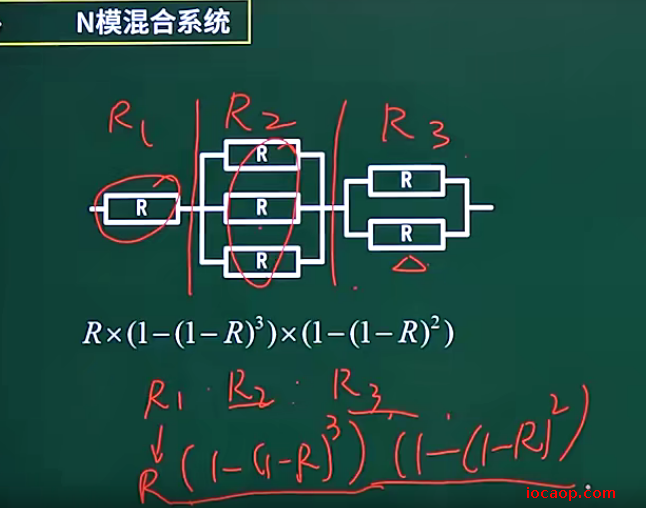

串联:R1到R所有系统都可用才行,所以累乘

并联:只要有一个可用,整个系统就可用。所以用1减去所有系统都不可用的概率。

例题:

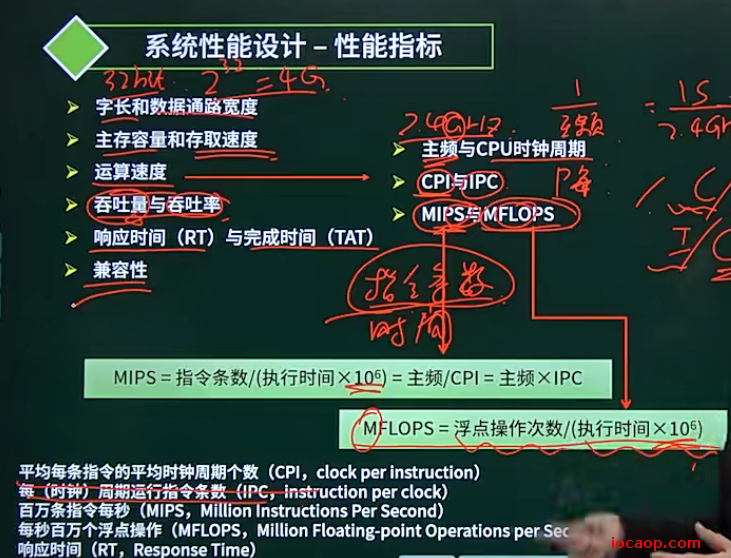

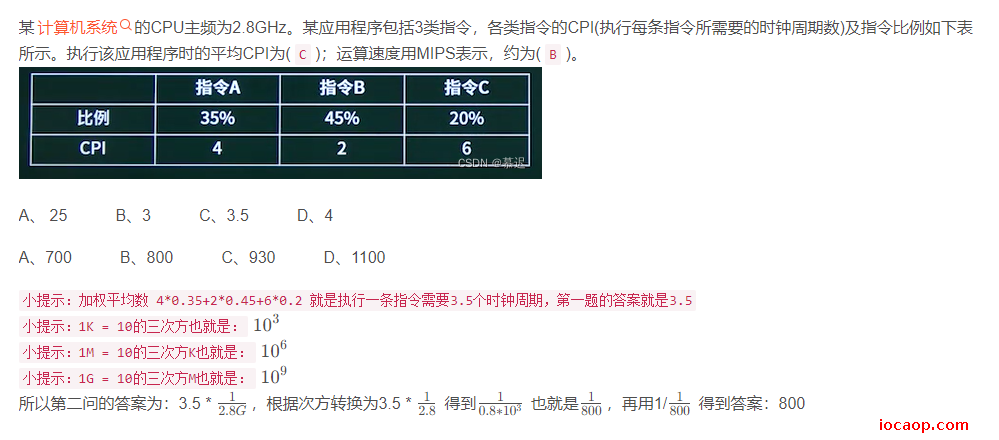

1.11-性能指标

例题:

注意约分和单位换算。

1.12-小结

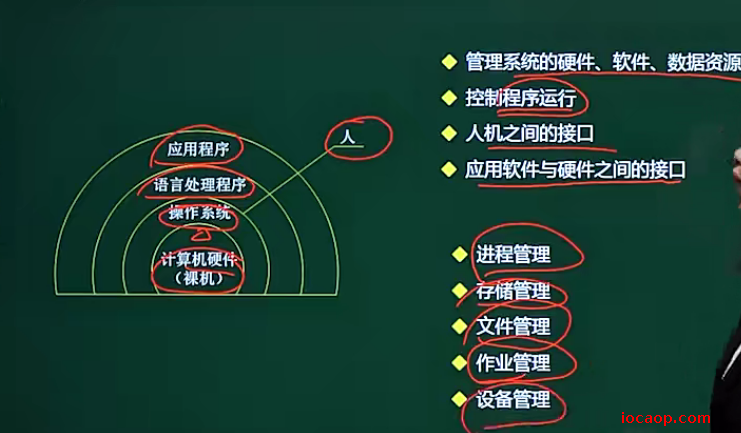

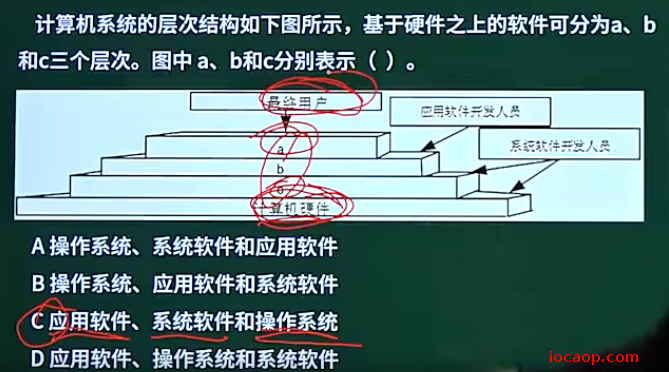

2.1 -操作系统概念

2.1.2-操作系统的作用

例题:

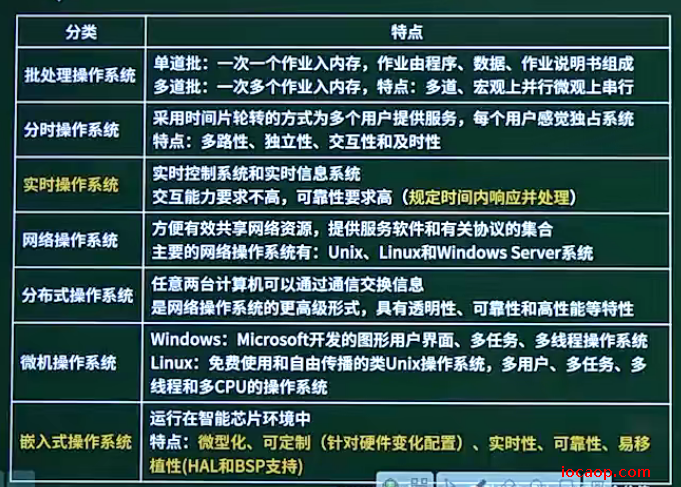

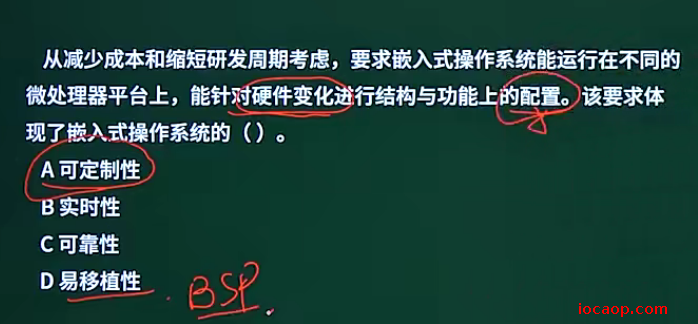

2.1.3-特殊的操作系统

例题:

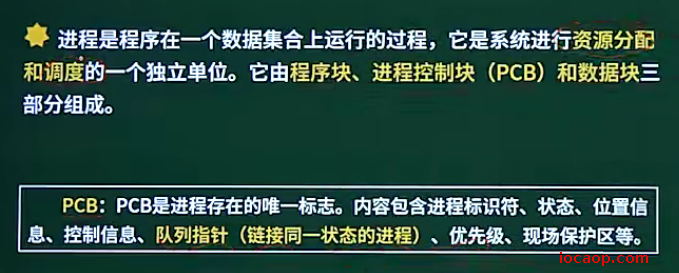

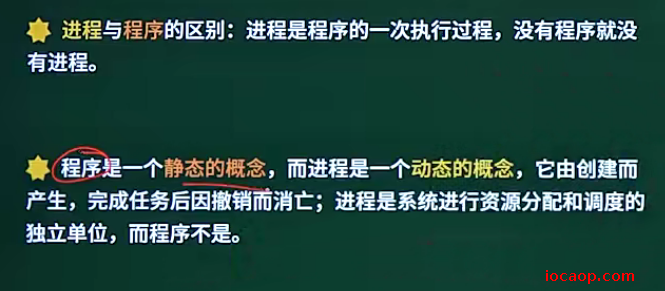

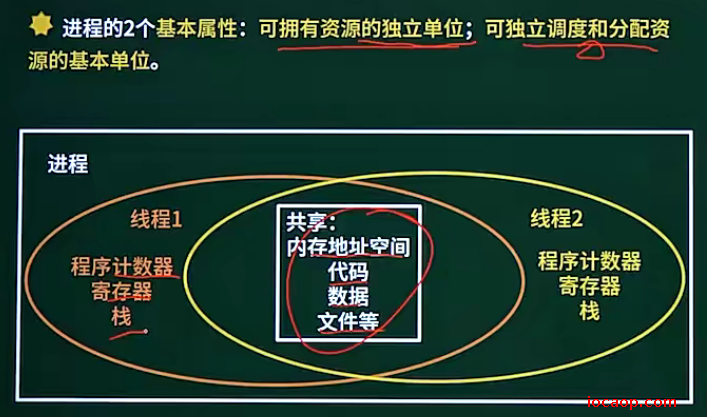

2.2进程的概念

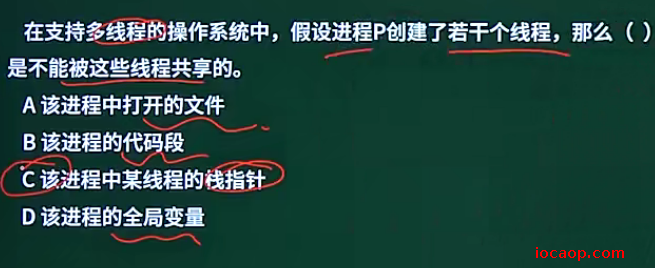

2.2.2-线程概念

例题:

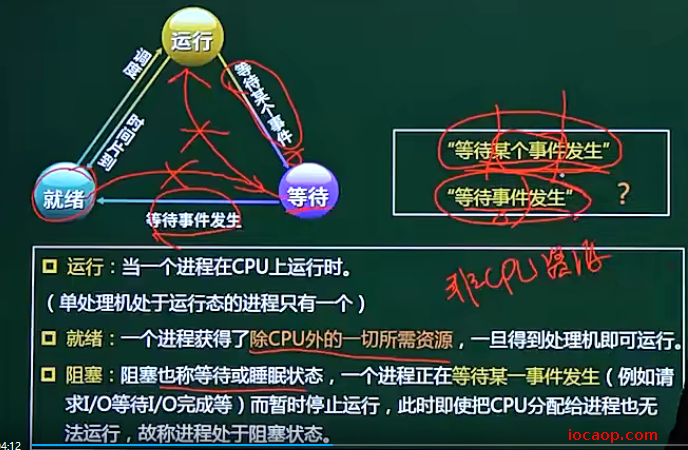

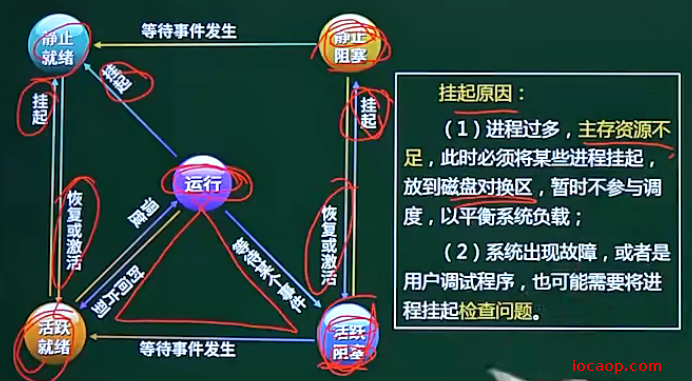

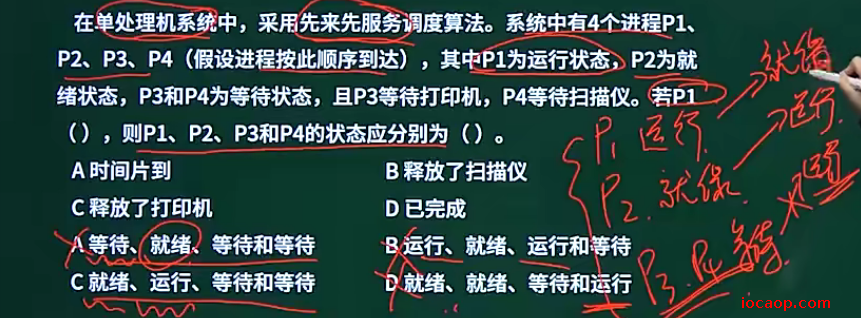

2.2.3-进程的状态

三状态模型:

例题:

首先,单处理机,排除B,不可能有2个运行的。

再排除D,p3和p4不可能直接从阻塞变成运行。

然后排除A,如果p1变为就绪或者等待,那么p2一定会变为运行。

然后得出第一空,时间片到了,p1变为就绪。

2.3-进程调度

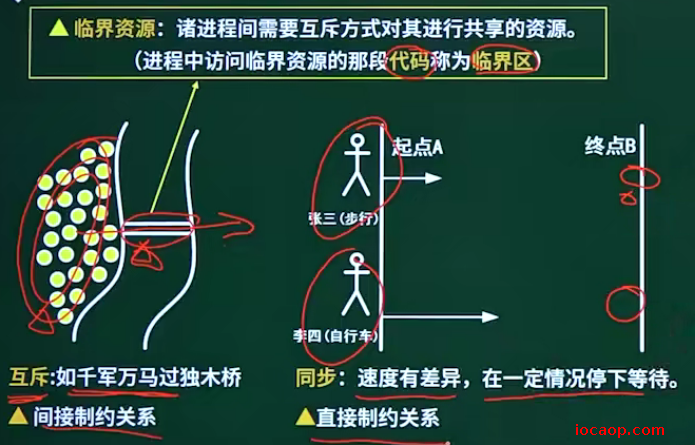

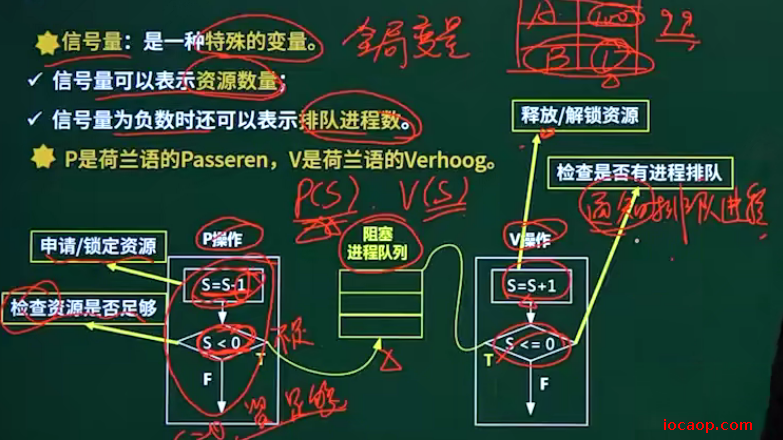

2.3.2-PV原语概述

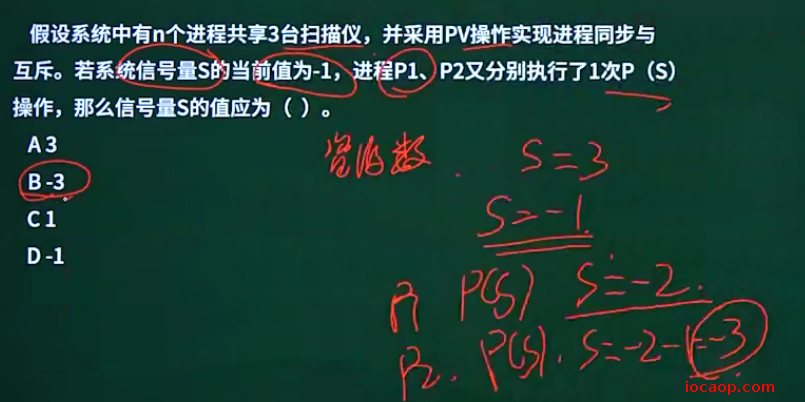

信号量的值一般设置为资源的数量。

P是加锁,v是解锁。

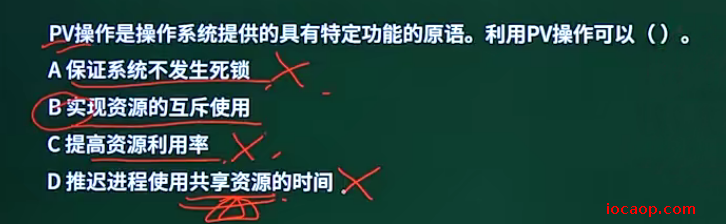

例题:

2.2.3-信号量和PV操作

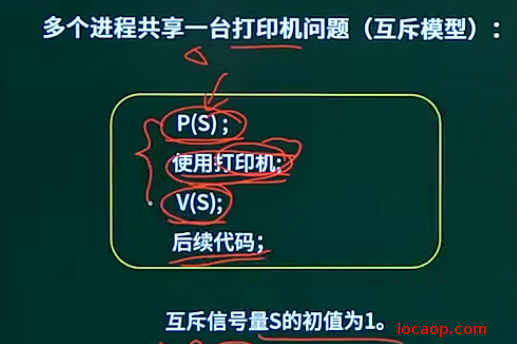

互斥模型:

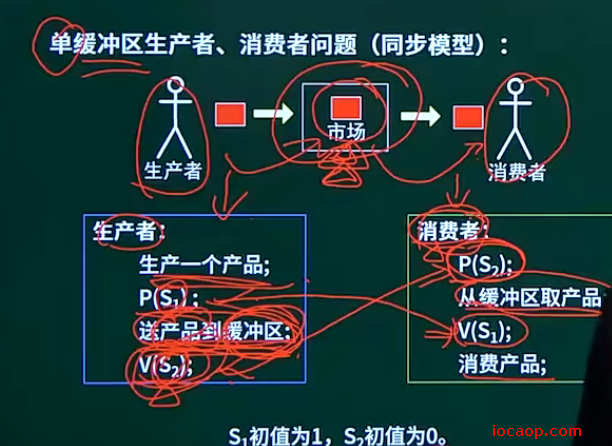

同步模型:

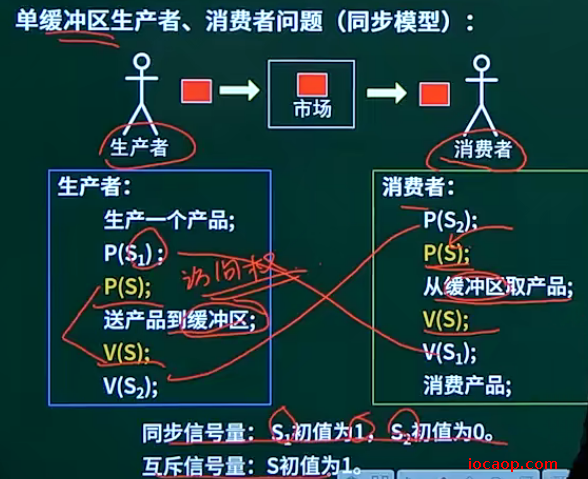

综合模型:

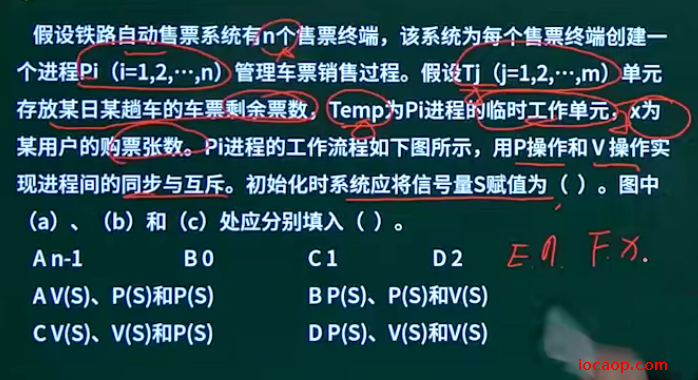

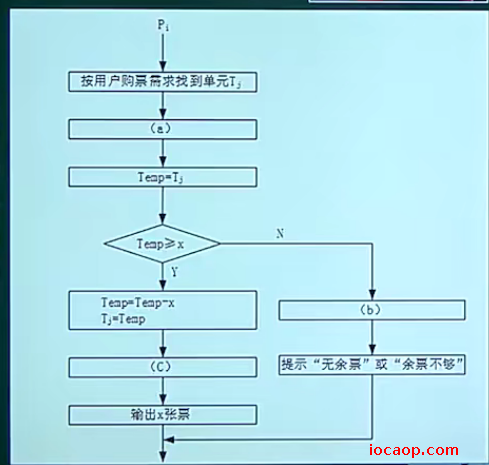

例题:

s信号量应该是临界资源的数据,只有一个Temp,所以s初始值为1

a处应该对temp加锁,b、c两处都是释放锁,只是处于不同情况下。

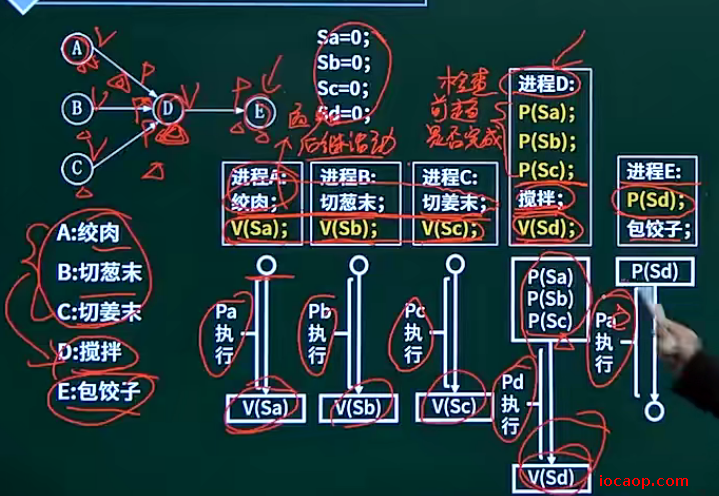

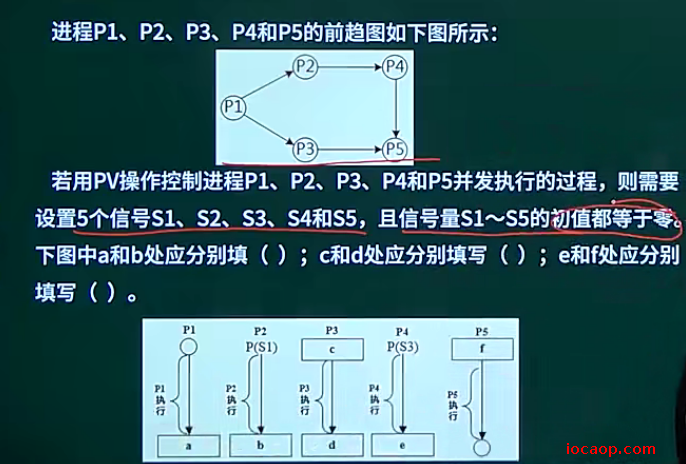

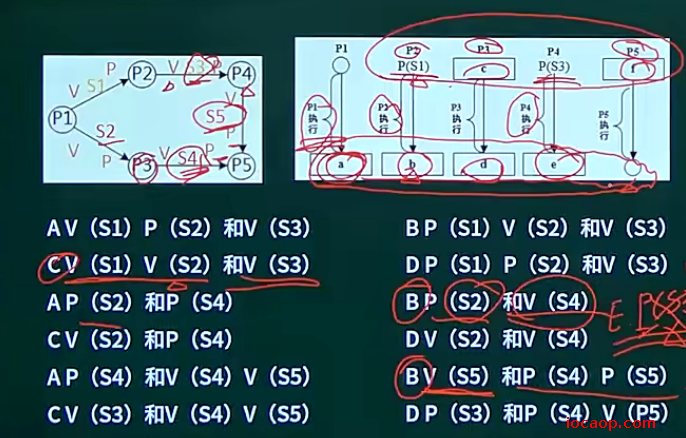

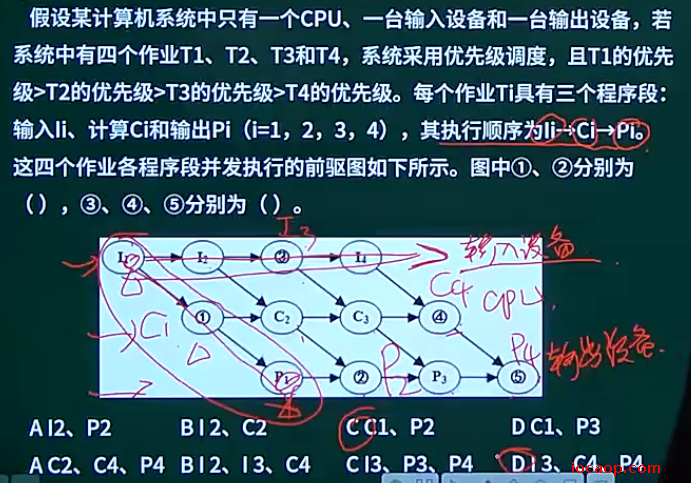

2.3.4-前驱图与PV操作

例题:

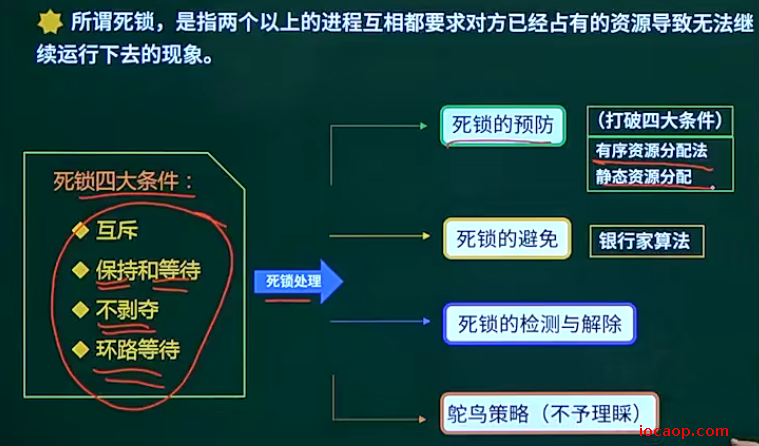

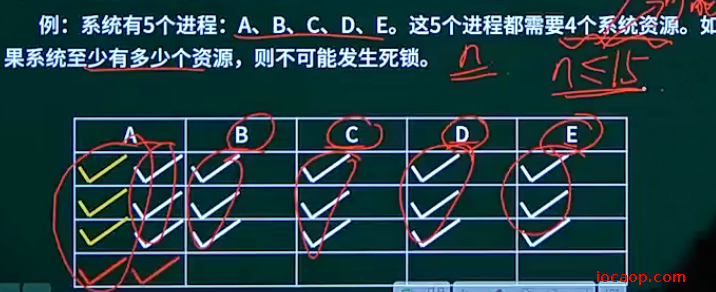

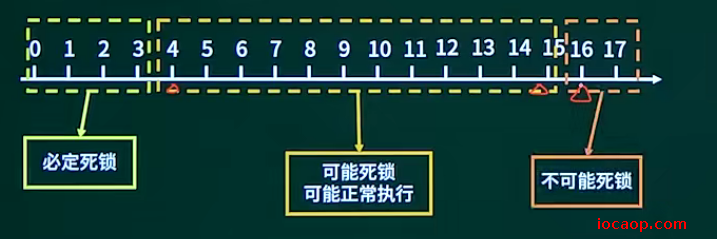

2.4-死锁资源数的计算

最乐观的情况,4个资源都在同一个进程。

最悲观的情况,5个进程都刚好差1个资源。

所以,在最悲观的情况加额外增加一个资源就可以避免死锁了。

得出公式:

W:每个进程执行所需资源数

M:进程数

N:总的可用资源数

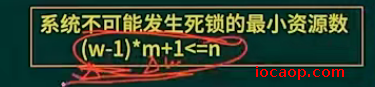

例题:

代公式

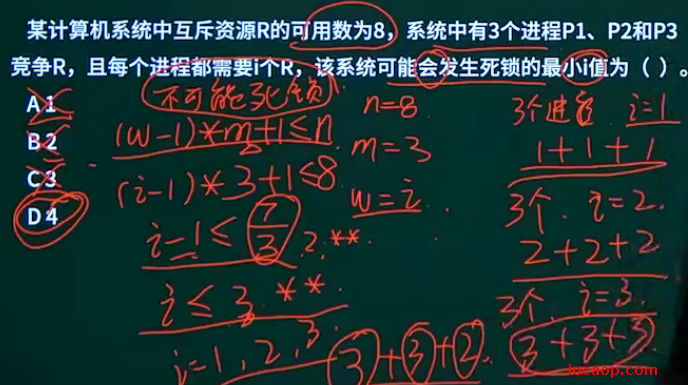

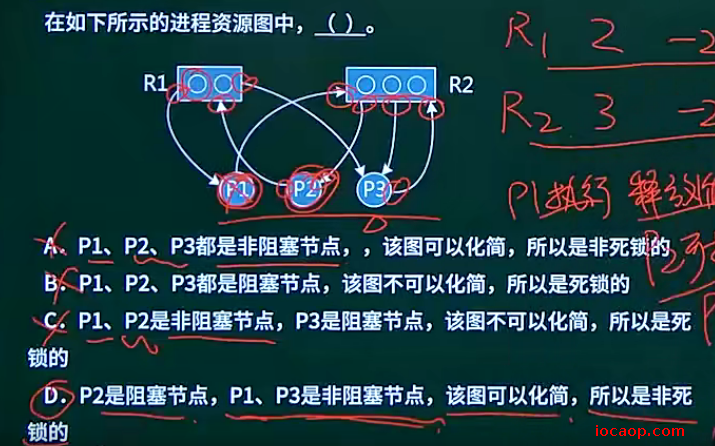

2.5-进程资源图

例题:

这种题,先看资源分配,R1和R2向外分配了多少,然后算出R1和R2剩余资源数,然后再来看申请资源,够不够,如果不够就是阻塞节点,足够就是非阻塞节点,如果非阻塞节点执行完后释放资源可以满足其他节点执行,就可以一步步化简。

2.6-段页式存储

2.6.1-概述

缺页中断就是要访问的页不在主存,需要操作系统将其调入主存后再进行访问。

调入的方式有:

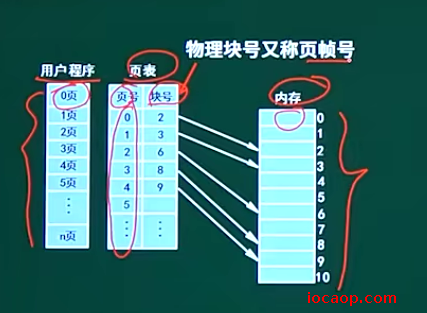

2.6.2-页式存储

将用户程序划分成和内存相同大小的页,页里面有相同大小的块。

在用户程序中使用逻辑地址:由页号+页内地址

实际的物理地址是:页帧号+业内地址

缺页中断时,将用户程序调入内存,逻辑地址是已知的,要将逻辑地址转换为物理地址。

在逻辑地址转换为物理地址的过程中,页号和页帧号的对应关系已经记录在页表中。页内地址是不会发生变化的。因为划分页时,大小是固定的,且用户程序划分的大小和物理内存划分大小是一致的。